| 自编教材 |

二、TEC-9实验系统的组成

TEC-9实验系统由以下几个部分组成:

控制台

数据通路

控制器

时序电路

数字逻辑实验区

电源模块

下面分别对各组成部分予以介绍。

1、电源

电源部分由一个电源、一个电源插座、一个电源开关和一个红色电源指示灯组成。电源通过四个螺钉安装在实验箱底部,它输出+5V电压,最大负载电流3A,具有抗+5V对地短路功能。电源插座用于接交流220V,插座内装有保险丝。电源开关接通时,模块电源输出+5V,红色指示灯点亮。

2、时序发生器

时序发生器产生计算机模型所需的时序和数字逻辑实验所需的时钟。时序电路由一个500KHz晶振、2片GAL22V10组成。根据本机设计,执行一条微指令需要4个节拍脉冲T1、T2、T3、T4,执行一条机器指令需要三个节拍电位W1、W2、W3,因此本机的基本时序如下:

图中,MF是晶振产生的500KHz基本时钟,T1、T2、T3、T4是数据通路和控制器中各寄存器的节拍脉冲信号,印制板上已将它们和相关的寄存器相连。T1、T2、T3、T4既供微过程控制器使用,也供硬连线控制器使用。W1、W2、W3,只供硬连线控制器做节拍电位信号使用。

3、数据通路

TEC-9的数据通路采用了数据总线和指令总线双总线形式。它还使用了大规模在系统编程器件作为寄存器堆,使得设计简单明了,可修改性强。

图1.2是数据通路总体图,下面介绍图中各个主要部件的作用。

1).运算器ALU

运算器ALU由两片74LS181组成,在选择端M和S0-S3控制下,ALU对数据A、B进行各种算术、逻辑运算。有关74181运算的具体操作,请看74181的资料和教科书。当LDRi=1时,在T4的上升沿寄存器C保存运算产生的进位标志信号。

2).运算操作数寄存器DR1和DR2

DR1和DR2是运算操作数寄存器,DR1和ALU的B口相连,DR2和ALU的A口相连。DR1和DR2各由2片74LS298构成。当M1=0且LDDR1=1时,在T3的下降沿,DR1接收来寄存器堆B端口的数据,当M1=1且LDDR1=1时,在T3的下降沿,DR1接收来自数据总线DBUS的数据。当M2=0且LDDR2=1时,在T3的下降沿,DR2接收来自通用寄存器堆A端口的数据。当M2=1且LDDR2=1时,在T3的下降沿,DR2接收来自数据总线DBUS的数据。

3).多端口通用寄存器堆RF

双端口通用寄存器堆RF由一片ispLSI1016构成,其中包含4个8位寄存器(R0、R1、R2、R3),有三个控制端口:两个控制读操作,一个控制写操作,三个端口可以同时操作。由RD1、RD0选中的寄存器的数据从A端口读出,由RS1、RS0选中的寄存器的数据从B端口读出;WR1、WR0选择要写入的寄存器。WRD控制写操作,当WRD=1时,在T2上升沿将来自ER寄存器的数据写入由WR1、WR0选中的寄存器。

从RF的A端口读出的数据直接送DR2。由B端口读出的数据直接送DR1之外,还可以送数据总线DBUS。当RS_BUS=1时,允许B端口数据送DBUS。

4).暂存寄存器ER

暂存寄存器ER是一片74LS374,主要用于暂时保存运算器的结果。当LDER=1时,在T4的上升沿,将数据总线DBUS上的数据打入暂存寄存器ER。ER的输出送往多端口通用寄存器堆RF,作为写入数据使用。

5).开关寄存器SW_BUS

开关寄存器SW_BUS是一片74LS244,用于将控制台数据开关SW7~SW0的数据送往数据总线DBUS。当SW_BUS=1时,允许开关SW7~SW0的数据送往总线DBUS。

6).双端口存储器RAM

双端口存储器RAM由一片IDT7132及少量控制电路构成。IDT7132是2048字节的双端口静态随机存储器,本实验系统实际使用256字节。IDT7132的两个端口可以同时进行读、写操作,在本实验系统中,RAM左端口连接数据总线DBUS,可进行读、写操作;右端口连接指令总线IBUS,输出到指令寄存器IR,作为只读端口使用。IDT7132有6个控制引脚,CEL、LRW、OEL控制左端口读、写操作;CER、RRW、OER控制右端口的读写操作。CEL为左端口选择引脚,高电平有效;当CEL=0时,禁止对左端口的读、写操作。LRW控制对左端口的读写。当CEL=1且LRW=1时,左端口进行读操作;当CEL=1且LRW=0在T3的上升沿左端口进行写操作。OEL的作用等同于三态门,当CEL=1且OEL=0时,允许左端口读出的数据送到数据总线DBUS上;当OEL=1时,禁止左端口的数据放到DBUS。本实验系统中左端口OEL由LRW经反相产生,不需单独控制。控制右端口的三个引脚与左端口的三个完全类似,不过只使用了读操作,在实验板上已将RRW固定接高电平,OER固定接地。当CER=1时,右端口读出的数据(更确切的说法是指令)放到指令总线IBUS上,然后当LDIR=1时在T3的上升沿打入指令寄存器IR。所有数据/指令的写入都使用左端口,右端口作为指令端口,不需要进行数据的写入。

左端口读出的数据放在数据总线DBUS上,由数据总线指示灯DBUS7-DBUS0显示。右端口读出的指令放在指令总线IBUS上,由指令总线指示灯IBUS7-IBUS0显示。

7).地址寄存器AR1和AR2

地址寄存器AR1和AR2提供双端口存储器的地址。AR1是1片GAL22V10,具有加1功能,提供双端口存储器左端口地址,AR1从数据总线DBUS接收数据。AR1的控制信号是LDAR1和AR1_INC。当AR_INC=1时,在T4的上升沿,AR1的值加1;当LDAR1=1时,在T4的上升沿,将数据总线DBUS的数据打入地址寄存器AR1。AR2由2片74LS298组成,有两个数据输入端,一个来自程序计数器PC,另一个来自数据总线DBUS。AR2的控制信号是LDAR2和M3。M3选择数据来源,当M3=1时,选中数据总线DBUS;当M3=0时,选中程序计数器PC。LDAR2控制何时接收地址,当LDAR2=1时,在T2的下降沿将选中的数据源上数据打入AR2。

8).程序计数器PC、地址加法器ALU2、地址缓存器R4

程序计数器PC、地址加法器ALU2、地址缓存器R4联合完成三种操作:PC加载

PC+1、PC+D。

R4是由2片74LS298构成的具有存储功能的两路选择器,当M4=1时,选中数据总线DBUS;当M4=0时,从指令寄存器IR的低4位IR3~IR0接收数据。当LDR4=1时,在T2的下降沿将选中的数据打入R4。

ALU2是由一片GAL22V10构成,当PC_ADD=1时,完成PC和IR低4位的相加,即PC+D。

程序计数器PC是由一片GAL22V10构成,当PC_INC=1时,完成PC+1;当PC_ADD=1时,与ALU2一起完成PC+D的功能;当LDPC=1时,接收从ALU2和R4来的地址,实验是接收来数据总线DBUS的地址,这些新的程序地址在T4的上升沿打入PC寄存器。

9).指令寄存器IR

指令寄存器IR是一片74LS374。当LDIR=1时,在T4的上升沿,它从双端口存储器的右端口接收指令。指令的操作码部分IR7—IR4送往控制器译码,产生数据通路的控制信号。指令的操作数部分送往寄存器堆RF,选择参与运算的寄存器。IR1、IR0与RD1、RD0连接,选择目标操作数寄存器;IR3、IR2与RS1、RS0连接,选择源操作数寄存器。IR1、IR0也与WR1、WR0连接,以便将运算结果送往目标操作数寄存器。

本实验系统设计了11条基本的机器指令,均为单字长(8位)指令,指令功能及格式如下表所示,。另一点需说明的是:为了简化运算,指令JC D中的D是一个4位的正数,用D3~D0表示。

表1机器指令系统

名称 | 助记符 | 功能 | 指令格式 | ||

IR7 IR6 IR5 IR4 | IR3 IR2 | IR1 IR0 | |||

加法 | ADD Rd, Rs | Rd + Rs→Rd | 0 0 0 0 | Rs1 Rs0 | Rd1 Rd0 |

减法 | SUB Rd, Rs | Rd - Rs→Rd | 0 0 0 1 | Rs1 Rs0 | Rd1 Rd0 |

逻辑与 | AND Rd, Rs | Rd & Rs→Rd | 0 0 1 1 | Rs1 Rs0 | Rd1 Rd0 |

存数 | STA Rd, [Rs] | Rd→[Rs] | 0 1 0 0 | Rs1 Rs0 | Rd1 Rd0 |

取数 | LDA Rd, [Rs] | [Rs]→Rd | 0 1 0 1 | Rs1 Rs0 | Rd1 Rd0 |

无条件转移 | JMP [RS] | [RS] →PC | 1 0 0 0 | Rs1 Rs0 | X X |

条件转移 | JC D | 若C=1 则PC=D→PC | 1 0 0 1 | D3 D2 | D1 D0 |

停机 | STP | 暂停执行 | 0 1 1 0 | X X | X X |

中断返回 | IRET | 返回断点 | 1 0 1 0 | X X | X X |

开中断 | INTS | 允许中断 | 1 0 1 1 | X X | X X |

关中断 | INTC | 禁止中断 | 1 1 0 0 | X X | X X |

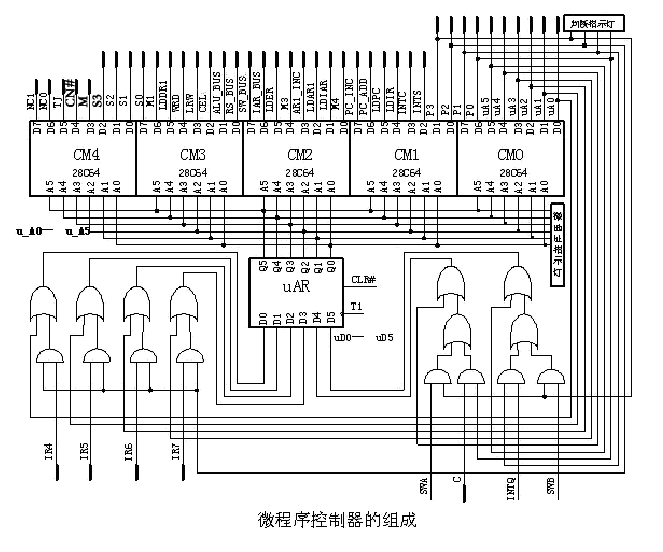

4、微程序控制器

控制器用来产生数据通路操作所需的控制信号。TEC-9提供了一个微程序控制器,以便能进行计算机组成原理基本实验。在进行课程设计时,学生可设计自己的控制器。图1.2是控制器框图。

1).控制存储器

控制存储器由5片HN58C65/28C64构成。HN58C65/28C64是E2PROM,存储容量为8K字节,本实验系统只使用了128字节。微指令格式采用水平型,微指令字长35位,其中顺序控制部分10位:判别字段4位,后继微地址6位。操作控制字段25位,各位进行直接控制。

判断标志位P3和控制台开关SWB、SWA结合在一起确定微程序的分支,完成不同的控制台操作。

判断标志位P2与指令操作码(IR的高4位IR7~IR4)结合确定微程序的分支。转向各种指令的不同微程序流程。

判断标志位P1标志一条指令的结束,与中断请求信号INTQ结合,实验对程序的中断处理。

判断标志位P0与进位标志C结合确定微程序的分支,实验条件转指指令。

操作控制字段25位,全部采用直接表示法,控制数据通路的操作。在设计过程中,根据微程序流程图对控制信号进行了适当的综合与归并,把某些在微程序流程图中作用相同或者类似的信号归并为一个信号。下面列出微程序提供的控制信号。

说明:书中微程序控制器EEPROM由58C64或28C64组成,可能是版本或生产时间不同而采用不同的芯片,两种芯片在性能上基本兼容。书中采用一种芯片介绍。

表1.2 控制信号表

S3,S2,S1,S0 | 选择运算器的运算类型。 |

M | 选择运算器的运算模式:M=0,算术运算;M=1,逻辑运算。 |

Cn# | 运算器最低位的 +1信号。为0时,运算器最低位有进位。 |

LRW | 当LRW=1且CEL=1时,对双端口存储器左端口进行读操作;当LRW=0且CEL=1时,对左端口进行写操作。 |

CEL | 双端口存储器左端口使能信号。为1时允许对左端口读、写。 |

CER | 双端口存储器右端口使能信号。为1时将指令送往指令总线IBUS。 |

M1(M2) | 当M1=1时,操作数寄存器DR1从数据总线DBUS接收数据,当M1=0时,操作数寄存器DR1从寄存器堆RF接收数据。此信号也用于作为操作数寄存器DR2的数据来源选择信号。 |

ALU_BUS | ALU输出三态门使能信号,为1时将ALU运算结果送DBUS。 |

RS_BUS | 通用寄存器右端口三态门使能信号,为1时将RF的B端口数据送DBUS。 |

SW_BUS | 控制台输出三态门使能信号,为1时将控制台开关SW7-SW0数据送DBUS。 |

WRD | 双端口寄存器堆写入信号,为1时将数据总线上的数据在T2的上升沿写入由WR1、WR0指定的个寄存器。 |

LDDR2 | 对操作数寄存器DR2进行加载的控制信号,为1时在T3的下降沿将由RS1、RS0指定的寄存器中的数据打入DR2。 |

LDDR1 | 对操作数寄存器DR1进行加载的控制信号,为1时在T3的下降沿将由RD1、RD0指定的寄存器中的数据打入DR1。 |

LDAR1(LDAR2) | 对地址寄存器AR1进行加载的控制信号。此信号也可用于作为允计对地址寄存器AR2加载。 |

AR1_INC | 对AR1进行加1操作的电位控制信号。 |

LDPC(LDR4) | 为1时,对程序计数器PC进行加载。此信号也用于作为R4的加载允许信号LDR4 |

PC_INC | 为1时,对PC进行加1操作的电位控制信号。 |

LDIR(CER) | 为1时,对指令寄存器进行加载的控制信号。 在T4上升沿保存C、Z标志位。 |

INTS | 置中断允计标志INTE为1 |

INTC | 清除中断允许标志INTE |

M4 | 当M4=1时,R4从数据总线DBUS接收数据。 当M4=0时,R4从指令寄存器IR接收数据。 |

M3 | 当M3=1时,AR2从数据总线DBUS接收数据。 当M3=0时,AR2从程序计数器PC接收数据 |

LDER | 为1时,允许对暂存寄存器ER加载;在T4的上升沿保存C、Z标志位 |

LDIAR | 为1时,对中断寄存器IAR加载。 |

TJ | 停机指令,暂停微程序运行。 |

2).微地址寄存器μAR

微地址寄存器μAR是1片74LS273,对控制存储器提供微程序地址。当CLR#=0时,将异步清零,使微程序从000000B开始执行。在每一个T1的上升沿,新的微指令地址打入微地址寄存器中。微地址由指示灯uA5-uA0显示。控制台信号SWC直接连接74LS273,作为uD6,用于实验读寄存器操作。

3).微程序地址译码电路

微程序地址译码电路产生后继微程序地址,它由2片74LS32和2片74LS08构成。微程序地址译码电路数据来源是:控制存储器产生的后继微程序地址uA5~uA0,控制存储器产生的标志位P3~P0,指令操作码IR7~IR4,进位标志位C,中断请求标志INTQ,控制台方式标志位SWB、SWA。

5、控存EEPROM的改写

TEC-9中的5片EEPROM(CM4-CM0)是控存,里面装有微程序的微代码。由于它是电可擦除和编程的EEPROM,因此可以实现不用将CM4-CM0从插座上取出就能实现对其编程的目的。

6、控制台

控制台由若干拨动开关和指示灯组成,用于设置控制台指令、人工控制数据通路、设置数据代码信号和显示相关数据组成等。

1).数据开关SW7-SW0

八位数据开关,通过74LS244接到数据通路部分的数据总线DBUS上,用于向数据通路中的寄存器和存储器置数。当SW_BUS=1时,SW7

SW0的数据送往数据总线DBUS。开关拨到上面位置时输出1,开关拨到下面位置时输出0。SW7对应DBUS最高位,SW0对应DBUS最低位。

2).模拟数据通路控制信号开关K15-K0

拨动开关,拨到上面位置输出1,拨到下面位置输出0。实验中用于模拟数据通路部分所需的电平控制信号。例如,将K1与LDDR1相连,则K1拨到上面位置时,表示LDDR1为1。这些开关在数字逻辑与数字系统实验时也作为电平输入开关。

3).数据总线指示灯DBUS

八个发光二极管(高四位为红,低四位为绿),指示DBUS上数据。灯亮表示1。

4).指令总线指示灯IBUS

八个发光二极管(高四位为红,低四位为绿),指示IBUS上数据。灯亮表示1。

5).地址指示灯AR

八个发光二极管(高四位为红,低四位为绿),指示双端口存储器的左端口地址寄存器内容。灯亮表示1。

6).程序计数器指示灯PC

八个发光二极管(高四位为红,低四位为绿),指示双端口存储器右端口地址。灯亮表示1。

7).40位微命令指示灯CM3-CM0

40个红色发光二极管,显示从控制存储器读出的微命令的内容。

8).其它指示灯C、BUSYL、BUSYR

C是进位标志指示灯。BUSYL、BUSYR分别是RAM左右端口忙指示灯。

9).运算器指令灯

A7~A0,运算器A口数据指指示灯;B7~B0,运算器B口数据指示灯;F7~F0,运算器运算结果输出数据指示灯

10).微动开关CLR#、QD

按一次CLR#开关,产生一个负的单脉冲CLR#,正的单脉冲CLR。CLR#对全机进行复位。CLR#到时序和控制器的连接已经在印制板上实现,控制存储器和数据通路部分不使用CLR#。按一次QD按钮,产生一个正的启动脉冲QD和负的单脉冲QD#。QD使机器运行。

11).工作方式选择开关

a、工作模式设置开关

SWC SWB SWA | 功能 |

0 0 0 | 启动程序:程序从指定的地址开始运行 |

0 0 1 | 读双端口存储器 |

0 1 0 | 写双端口存储器 |

0 1 1 | 写寄存器堆 |

1 0 0 | 读寄存器堆 |

启动程序(PR):按下复位按钮CLR#后,微地址寄存器清零。这时, SWC=0、SWB=0、SWA=0,用数据开关SW7

SW0设置RAM中的程序首地址,按QD按钮后,启动程序执行。

写存储器(WRM):按下复位按钮CLR#,置SWC=0、SWB=1、SWA=0。①在SW7

SW0中置好存储器地址,按QD按钮将此地址打入AR1。②在SW7

SW0置好数据,按QD,将数据写入AR1指定的存储器单元,这时AR加1。③返回②。依次进行下去,直到按复位键CLR#为止。这样就实现了对RAM的连续手动写入。这个控制台操作的主要作用是向RAM中写入自己编写的程序和数据。

读存储器(RRM):按下复位按钮CLR#,置SWC=0、SWB=0、SWA=1。①在SW7

SW0中置好存储器地址,按QD按钮将此地址打入AR1,RAM此地址单元的内容读至DBUS显示。②按QD按钮,这时AR1加1,RAM新地址单元的内容读至DBUS显示。③返回②。依次进行下去,直到按复位键CLR#为止。这样就实现了对RAM的连续读出显示。这个控制台操作的主要作用是检查写入RAM的程序和数据是否正确。在程序执行后检查程序执行的结果(在存储器中的部分)是否正确。

寄存器写操作(WRF):按下复位按钮CLR#,置SWC=0、SWB=1、SWA=1。①首先在SW7—SW0置好存储器地址,按QD按钮,则将此地址打入AR1寄存器和AR2寄存器。②在SW1、SW0置好寄存器选择信号WR1、WR0,按QD按钮,通过双端口存储器的右端口将WR1、WR0(即SW1、SW0)送到指令寄存器IR的低2位。③在SW7

SW0中置好要写入寄存器的数据;按QD按钮,将数据写入由WR1、WR0指定的寄存器。④返回②继续执行,直到按复位按钮CLR#。这个控制台操作主要在程序运行前,向相关的通用寄存器中置入初始数据。

说明:第①、②操作是为了实现写一条写寄存器号指令,先在存储器写好地址,再将段写的有效寄存器号写入存储器,并从指令端口读出到指令总线

寄存器读操作(RRF):按下复位按钮CLR#,置SWC=1、SWB=0、SWA=0。①首先在SW7—SW0置好存储器地址,按QD按钮,则将此地址打入AR1寄存器和AR2寄存器。②在SW3、SW2置好寄存器选择信号RS1、RS0,按QD按钮,通过双端口存储器的右端口将RS1、RS0(即SW3、SW2)送到指令寄存器IR的第3、2位。RS1、RS0选中的寄存器的数据读出到DBUS上显示出来。③返回②继续下来,直到按复位键CLR#为止。这个控制台操作的主要作用是在程序执行前检查写入寄存器堆中的数据是否正确,在程序执行后检查程序执行的结果(在寄存器堆中的部分)是否正确。

说明:同上面写寄存器说明

b、控制器选择开关

微程序:选择控制器为微过程控制器,将自动一一对应连接好微程序信号与数据通路信号。

脱机: 微过程控制器、数据通路、硬布线控制器三部分信号完全独立。

硬布线:选择控制器为硬布线控制器,将自动一一对应连接好硬布线控制器与数据通路间的信号.

c、 DP、DZ、DB三个开关只能有一个为高有效。

DP DZ DB | 功能 |

0 0 0 | 连续运行 |

0 0 1 | 单步工作方式。硬布线 |

0 1 0 | 单指:运行一条指令。 |

1 0 0 | 单拍 |

DP(单拍)、DB(单步)是两种特殊的非连续工作方式。当DP=1时,计算机处于单拍工作方式,按一次QD按钮,只发送一组时序信号T1-T4,执行一条微指令。

DB方式只对硬连线控制器适用,当DB=1时,按一次QD按钮,发送一组W1-W3,执行一条机器指令。当DP=0且DB=0时,DZ=0时,TEC-9处于连续工作方式,按QD按钮,连续执行双端口RAM中存储的程序。

7、硬连线控制器EPM3128

EPM3128是Altera公司的1个在系统可编程器件,包含有2500门,适用于设计大规模的数字逻辑与数字系统电路。在计算机模型实验中,它用作设计并实现硬连线控制器,代替出厂时提供的微过程控制器。它有1个下载插座,下载时下载电缆的一端插在下载插座上,另一端插在PC机并行口上,下载电缆将PC机和EMP3128连在一起。在PC机上运行QUARTUS II工具软件,输入控制器的设计方案,进行编译、连接和适配,然后下载到EPM3128中去,就构成了1个硬连线控制器。硬连线控制器和数据通路部分采用可插、拔的导线连接或通过控制器选择开关选通。

8、数字逻辑和数字系统试验区

这部分为用户提供了通用的数字逻辑和数字系统实验平台。它主要包括下列部分:实验台左半部的11个双列直插插座,EPM3128在系统编程芯片及下载插座,6个数码管及其驱动电路,12个数据指示灯,小喇叭及其驱动电路,12个拨动开关,2个单脉冲按钮。

1)、双列直插插座

这一部分在实验台的左上部,实验时用于插中、小规模数字逻辑器件。注意:插座的电源和地都没有连接。

、CPLD

它位于实验台的左下部,用于设计并实现复杂的数字逻辑或数字系统电路和硬布线控制设计实验。

、7个数码管及其驱动电路。

为了能做较复杂的实验,比如电子时钟和数字频率计等实验,实验台上安装了7个数码管。7个数码管位于实验台的上部中间。左边3个数码管各由一片BCD七段译码器/驱动器74LS47驱动。只需在各数码管的4个输入插孔(D为最高位,A为最低位)接入BCD码,数码管就显示出相应数字。右边的4个数码管由1片74LS244驱动,可按段和位进行控制。它的段码控制端为a、b、c、d、e、f、g、h。当控制端接高电平时,则相应的发光二极管段点亮;当控制端接低电平时,相应的发光二极管熄灭。它的位码控制端为S3、S2、S1、S0,当控制端接高电平时,则相应的位有效。

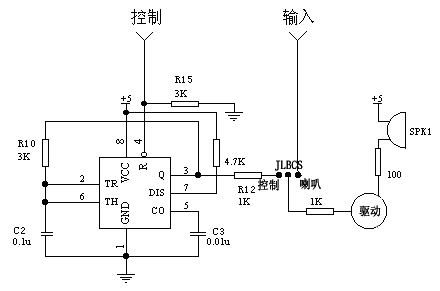

4)、小喇叭及驱动电路

这部分由可控振荡电路,喇叭及其驱动电路组成。电路如图1.4所示。

图1.4小喇叭及驱动电路

当JLBCS用短路片短接“控制”一侧时,它是一个可控声源,可做报警或者报时使用。如果“控制”插孔接高电平,则振荡电路输出频率为20Hz左右的方波,驱动喇叭鸣叫。当控制插孔接为低电平时,振荡电路输出低电平,喇叭

鸣叫。

当JLBCS用短路子短接“喇叭”一侧时,可从“喇叭”插孔向喇叭的驱动电路送控制信号。直接控制喇叭按希望的频率变化发声,做音乐实验用。

5)、单脉冲按钮

计算机组成原理实验中使用的启动按钮QD和复位按钮CLR#及一路单独的单脉冲。在数字逻辑和数字系统实验中作为单脉冲按钮使用。每个按钮按下后都能输出1个正脉冲和1个负脉冲。不过由于在计算机组成原理中,QD按钮使用的是正脉冲,CLR#按钮使用的是负脉冲,因此在数字逻辑和数字系统实验中,最好使用QD按钮产生的负脉冲和CLR#按钮产生的正脉冲。单独的单脉冲可用于控制器实验中的中断申请,或数字电路实验。

6)、电平开关K0-K15

在计算机组成原理实验中使用的模拟数据通路控制信号开关K15-K0在数字逻辑和数字系统实验中作为普通的电平开关使用。

7)、10个发光二极管

10个发光二极管位于TEC-9实验板的左上部位置,用于指示信号的高低电平,信号输入孔L0—L9接入高电平时,相应的二极管点亮,信号输入孔L0—L9接入低电平时,相应的二极管熄灭。

8)、逻辑笔

当输入端Ui接高电平时红灯(高)亮,接低电平时绿灯(低)亮。有一脉冲时,黄灯亮一次,计数指示灯加1。可以测试TTL电平和CMOS电平。

9)、峰鸣器

峰鸣器及驱动电路,可用作报警或提示实验。输入端接高电平时,峰鸣器发声。